# mmWave Radar Interface Control Document

Revision 2.23

Jul 22, 2022

#### Contents

|    |                           | Pa                                                     | age                |  |  |  |  |  |  |  |

|----|---------------------------|--------------------------------------------------------|--------------------|--|--|--|--|--|--|--|

| C  | onter                     | •                                                      | xi                 |  |  |  |  |  |  |  |

| Li | List of Figures xii       |                                                        |                    |  |  |  |  |  |  |  |

| Li | st of                     | ables                                                  | xvii               |  |  |  |  |  |  |  |

| Re | evisio                    | History                                                | xix                |  |  |  |  |  |  |  |

| 1  | <b>Intr</b><br>1.1<br>1.2 | luction<br>cope                                        | <b>1</b><br>1<br>2 |  |  |  |  |  |  |  |

| 2  | TI n                      | Wave Radar Sensor Communications Overview              | 3                  |  |  |  |  |  |  |  |

|    | 2.1                       | ommunication Link Description                          | 3                  |  |  |  |  |  |  |  |

|    | 2.2                       | ommunication Link configuration                        | 3                  |  |  |  |  |  |  |  |

|    |                           | .2.1 SPI                                               | 3                  |  |  |  |  |  |  |  |

|    |                           | .2.2 Mailbox                                           | 3                  |  |  |  |  |  |  |  |

|    | 2.3                       | adar Message Structure                                 | 5                  |  |  |  |  |  |  |  |

|    |                           | .3.1 SYNC                                              | 6                  |  |  |  |  |  |  |  |

|    |                           | .3.2 MSGHDR                                            | 6                  |  |  |  |  |  |  |  |

|    |                           | .3.3 MSGDATA                                           | 12                 |  |  |  |  |  |  |  |

|    |                           | .3.4 CRC                                               | 13                 |  |  |  |  |  |  |  |

| 3  | Mes                       | age Processing                                         | 15                 |  |  |  |  |  |  |  |

|    | 3.1                       | ommunication protocol                                  | 15                 |  |  |  |  |  |  |  |

|    | 3.2                       | ommunication Sequence                                  | 16                 |  |  |  |  |  |  |  |

|    |                           | .2.1 Command/Response Sequence (Host)                  | 16                 |  |  |  |  |  |  |  |

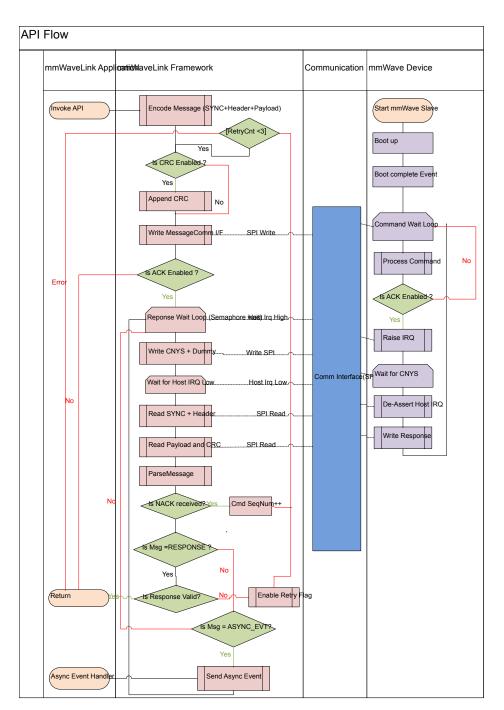

|    |                           | .2.2 Flow Diagram (Host) – Command/Response            | 17                 |  |  |  |  |  |  |  |

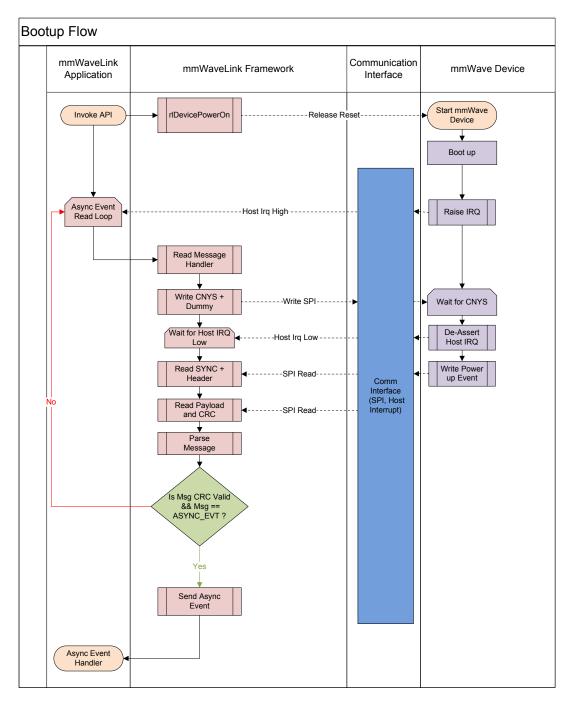

|    |                           | .2.3 Flow Diagram (Host) – Bootup/ Asynchronous Event  |                    |  |  |  |  |  |  |  |

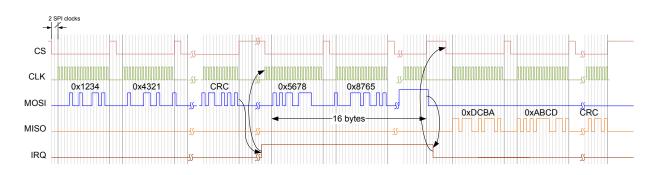

|    |                           | .2.4 SPI Message Sequence – Command/Response           | 19                 |  |  |  |  |  |  |  |

| 4  | Rac                       | r Interface Messages Descriptions                      | 21                 |  |  |  |  |  |  |  |

|    | 4.1                       | ummary of all messages and their associated sub-blocks | 21                 |  |  |  |  |  |  |  |

|    | 4.2                       | WR_ACK_MSG                                             | 27                 |  |  |  |  |  |  |  |

|   | 4.3        | AWR_N                                                                                                                  | ACK_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27                                                                                                                                 |

|---|------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   | 4.4        | AWR_EI                                                                                                                 | RROR_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                                                                 |

|   | 4.5        | AWR_R                                                                                                                  | F_STATIC_CONF_SET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28                                                                                                                                 |

|   | 4.6        | AWR_R                                                                                                                  | F_STATIC_CONF_GET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30                                                                                                                                 |

|   | 4.7        | AWR_R                                                                                                                  | F_INIT_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31                                                                                                                                 |

|   | 4.8        | AWR_R                                                                                                                  | F_DYNAMIC_CONF_SET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                                                                                                                                 |

|   | 4.9        | AWR_R                                                                                                                  | F_DYNAMIC_CONF_GET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                                                                                 |

|   | 4.10       | AWR_R                                                                                                                  | F_FRAME_TRIG_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33                                                                                                                                 |

|   | 4.11       | AWR_R                                                                                                                  | F_ADVANCED_FEATURES_CONF_SET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35                                                                                                                                 |

|   | 4.12       | AWR_R                                                                                                                  | F_MONITORING_CONF_SET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36                                                                                                                                 |

|   | 4.13       | AWR_R                                                                                                                  | F_STATUS_GET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37                                                                                                                                 |

|   | 4.14       | AWR_R                                                                                                                  | F_MONITORING_REPORT_GET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38                                                                                                                                 |

|   | 4.15       | AWR_R                                                                                                                  | F_MISC_CONF_SET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38                                                                                                                                 |

|   | 4.16       | AWR_R                                                                                                                  | F_MISC_CONF_GET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39                                                                                                                                 |

|   | 4.17       | AWR_R                                                                                                                  | F_ASYNC_EVENT_MSG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40                                                                                                                                 |

|   | 4.18       | AWR_R                                                                                                                  | F_ASYNC_EVENT_MSG2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41                                                                                                                                 |

|   | 4.19       | AWR_D                                                                                                                  | EV_RFPOWERUP_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42                                                                                                                                 |

|   | 4.20       | AWR_D                                                                                                                  | EV_CONF_SET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43                                                                                                                                 |

|   | 4.21       | AWR_D                                                                                                                  | EV_CONF_GET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44                                                                                                                                 |

|   | 4.22       | AWR_D                                                                                                                  | EV_FILE_DOWNLOAD_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                                                                                                                 |

|   | 4.23       | AWR_D                                                                                                                  | EV_FRAME_CONFIG_APPLY_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46                                                                                                                                 |

|   | 4.24       | AWR_D                                                                                                                  | EV_STATUS_GET_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46                                                                                                                                 |

|   | 4.25       | AWR_D                                                                                                                  | EV_ASYNC_EVENT_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47                                                                                                                                 |

| 5 | Rad        | lar Func                                                                                                               | tional APIs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49                                                                                                                                 |

| - |            |                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                    |

|   | 5.1        | Sub bloc                                                                                                               | ck related to AWR_ERBOR_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49                                                                                                                                 |

|   | 5.1        |                                                                                                                        | k related to AWR_ERROR_MSG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                    |

|   |            | 5.1.1                                                                                                                  | Sub block 0x0000 – AWR_RESP_ERROR_SB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49                                                                                                                                 |

|   | 5.1<br>5.2 | 5.1.1<br>Sub bloc                                                                                                      | Sub block 0x0000 – AWR_RESP_ERROR_SB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>50                                                                                                                           |

|   |            | 5.1.1                                                                                                                  | Sub block 0x0000 – AWR_RESP_ERROR_SB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>50<br>50                                                                                                                     |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1                                                                                             | Sub block 0x0000 – AWR_RESP_ERROR_SB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>50<br>50<br>53                                                                                                               |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1<br>5.2.2                                                                                    | Sub block 0x0000 – AWR_RESP_ERROR_SB         cks related to AWR_RF_STATIC_CONF_SET_MSG         Sub block 0x0080 – AWR_CHAN_CONF_SET_SB         Sub block 0x0082 – AWR_ADCOUT_CONF_SET_SB         Sub block 0x0083 – AWR_LOWPOWERMODE_CONF_SET_SB                                                                                                                                                                                                                                                                                                                                                           | 49<br>50<br>50<br>53<br>54                                                                                                         |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1<br>5.2.2<br>5.2.3                                                                           | Sub block 0x0000 - AWR_RESP_ERROR_SB         cks related to AWR_RF_STATIC_CONF_SET_MSG         Sub block 0x0080 - AWR_CHAN_CONF_SET_SB         Sub block 0x0082 - AWR_ADCOUT_CONF_SET_SB         Sub block 0x0083 - AWR_LOWPOWERMODE_CONF_SET_SB         Sub block 0x0084 - AWR_DYNAMICPOWERSAVE_CONF_SET_SB                                                                                                                                                                                                                                                                                               | 49<br>50<br>50<br>53<br>54<br>55                                                                                                   |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                                                         | Sub block 0x0000 – AWR_RESP_ERROR_SB         cks related to AWR_RF_STATIC_CONF_SET_MSG         Sub block 0x0080 – AWR_CHAN_CONF_SET_SB         Sub block 0x0082 – AWR_ADCOUT_CONF_SET_SB         Sub block 0x0083 – AWR_ADCOUT_CONF_SET_SB         Sub block 0x0083 – AWR_LOWPOWERMODE_CONF_SET_SB         Sub block 0x0084 – AWR_DYNAMICPOWERSAVE_CONF_SET_SB         Sub block 0x0085 – AWR_HIGHSPEEDINTFCLK_CONF_SET_SB                                                                                                                                                                                 | 49<br>50<br>53<br>53<br>54<br>55<br>56                                                                                             |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6                                                | Sub block 0x0000 – AWR_RESP_ERROR_SB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>50<br>53<br>54<br>55<br>56<br>56                                                                                             |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7                                       | Sub block 0x0000 - AWR_RESP_ERROR_SB         cks related to AWR_RF_STATIC_CONF_SET_MSG         Sub block 0x0080 - AWR_CHAN_CONF_SET_SB         Sub block 0x0082 - AWR_ADCOUT_CONF_SET_SB         Sub block 0x0083 - AWR_LOWPOWERMODE_CONF_SET_SB         Sub block 0x0084 - AWR_DYNAMICPOWERSAVE_CONF_SET_SB         Sub block 0x0085 - AWR_HIGHSPEEDINTFCLK_CONF_SET_SB         Sub block 0x0086 - AWR_RF_DEVICE_CFG_SB         Sub block 0x0087 - AWR_RF_RADAR_MISC_CTL_SB                                                                                                                               | 49<br>50<br>53<br>54<br>55<br>56<br>56<br>59                                                                                       |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6                                                | Sub block 0x0000 – AWR_RESP_ERROR_SB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ol> <li>49</li> <li>50</li> <li>50</li> <li>53</li> <li>54</li> <li>55</li> <li>56</li> <li>59</li> <li>61</li> </ol>             |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.6<br>5.2.7<br>5.2.8                     | Sub block 0x0000 - AWR_RESP_ERROR_SB         cks related to AWR_RF_STATIC_CONF_SET_MSG         Sub block 0x0080 - AWR_CHAN_CONF_SET_SB         Sub block 0x0082 - AWR_ADCOUT_CONF_SET_SB         Sub block 0x0083 - AWR_LOWPOWERMODE_CONF_SET_SB         Sub block 0x0084 - AWR_DYNAMICPOWERSAVE_CONF_SET_SB         Sub block 0x0085 - AWR_HIGHSPEEDINTFCLK_CONF_SET_SB         Sub block 0x0086 - AWR_RF_DEVICE_CFG_SB         Sub block 0x0087 - AWR_RF_RADAR_MISC_CTL_SB                                                                                                                               | <ol> <li>49</li> <li>50</li> <li>50</li> <li>53</li> <li>54</li> <li>55</li> <li>56</li> <li>59</li> <li>61</li> <li>63</li> </ol> |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9                     | Sub block 0x0000 – AWR_RESP_ERROR_SB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>50<br>53<br>54<br>55<br>56<br>59<br>61<br>63<br>63                                                                           |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9                     | Sub block 0x0000 - AWR_RESP_ERROR_SB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>50<br>53<br>54<br>55<br>56<br>59<br>61<br>63<br>62<br>64                                                                     |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>5.2.9<br>5.2.10  | Sub block 0x0000 - AWR_RESP_ERROR_SB<br>cks related to AWR_RF_STATIC_CONF_SET_MSG<br>Sub block 0x0080 - AWR_CHAN_CONF_SET_SB<br>Sub block 0x0082 - AWR_ADCOUT_CONF_SET_SB<br>Sub block 0x0083 - AWR_LOWPOWERMODE_CONF_SET_SB<br>Sub block 0x0084 - AWR_DYNAMICPOWERSAVE_CONF_SET_SB<br>Sub block 0x0085 - AWR_HIGHSPEEDINTFCLK_CONF_SET_SB<br>Sub block 0x0086 - AWR_RF_DEVICE_CFG_SB<br>Sub block 0x0087 - AWR_RF_RADAR_MISC_CTL_SB<br>Sub block 0x0088 - AWR_CAL_MON_FREQUENCY_LIMITS_SB<br>Sub block 0x0088 - AWR_CAL_MON_FREQUENCY_TX_POWER_LIMITS<br>SB                                               | 49<br>50<br>53<br>54<br>55<br>56<br>59<br>61<br>63<br>62<br>64                                                                     |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>5.2.10<br>5.2.11 | Sub block 0x0000 - AWR_RESP_ERROR_SB<br>cks related to AWR_RF_STATIC_CONF_SET_MSG<br>Sub block 0x0080 - AWR_CHAN_CONF_SET_SB<br>Sub block 0x0082 - AWR_ADCOUT_CONF_SET_SB<br>Sub block 0x0083 - AWR_LOWPOWERMODE_CONF_SET_SB<br>Sub block 0x0084 - AWR_DYNAMICPOWERSAVE_CONF_SET_SB<br>Sub block 0x0085 - AWR_HIGHSPEEDINTFCLK_CONF_SET_SB<br>Sub block 0x0086 - AWR_RF_DEVICE_CFG_SB<br>Sub block 0x0087 - AWR_RF_RADAR_MISC_CTL_SB<br>Sub block 0x0088 - AWR_CAL_MON_FREQUENCY_LIMITS_SB<br>Sub block 0x0088 - AWR_CAL_MON_FREQUENCY_TX_POWER_LIMITS<br>SB<br>Sub block 0x008B - AWR_CAL_DATA_RESTORE_SB | 49<br>50<br>53<br>54<br>55<br>56<br>59<br>61<br>63<br>62<br>64                                                                     |

|   |            | 5.1.1<br>Sub bloc<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>5.2.10<br>5.2.11 | Sub block 0x0000 – AWR_RESP_ERROR_SB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>50<br>53<br>54<br>55<br>56<br>59<br>61<br>63<br>64<br>66<br>67                                                               |

|     | 5.3.1    | Sub block 0x00A0 – 0x00AA – RESERVED                      |

|-----|----------|-----------------------------------------------------------|

|     | 5.3.2    | Sub block 0x00AB – AWR CAL DATA SAVE SB                   |

|     | 5.3.3    | Sub block 0x00AC – AWR_PHASE_SHIFTER_CAL_DATA_SAVE_SB 74  |

| 5.4 |          | cks related to AWR_RF_INIT_MSG                            |

| 0.4 | 5.4.1    | Sub block 0x00C0 – AWR RF INIT SB                         |

| 5.5 |          | cks related to AWR RF DYNAMIC CONF SET MSG                |

| 0.0 | 5.5.1    | Sub block 0x0100 – AWR PROFILE CONF SET SB                |

|     | 5.5.2    | Sub block 0x0101 – AWR CHIRP CONF SET SB                  |

|     | 5.5.3    | Sub block 0x0102 – AWR FRAME CONF SET SB                  |

|     | 5.5.4    | Sub block 0x0103 – AWR CONT STREAMING MODE CONF SET SB 94 |

|     | 5.5.5    | Sub block 0x0104 – AWR_CONT_STREAMING_MODE_EN_SB 97       |

|     | 5.5.6    | Sub block 0x0105 – AWR ADVANCED FRAME CONF SB 97          |

|     | 5.5.7    | Sub block 0x0106 – AWR PERCHIRPPHASESHIFT CONF SB 109     |

|     | 5.5.8    | Sub block 0x0107 – AWR PROG FILT COEFF RAM SET SB 111     |

|     | 5.5.9    | Sub block 0x0108 – AWR PROG FILT CONF SET SB              |

|     | 5.5.10   | Sub block 0x0109 – AWR CALIB MON TIME UNIT CONF SB 114    |

|     | 5.5.11   | Sub block 0x010A – AWR RUN TIME CALIBRATION CONF AND      |

|     |          | TRIGGER SB                                                |

|     | 5.5.12   | Sub block 0x010B – AWR DIGITAL COMP EST CONTROL SB 125    |

|     | 5.5.13   | Sub block 0x010C – AWR RX GAIN TEMPLUT SET SB             |

|     | 5.5.14   | Sub block 0x010D – AWR TX GAIN TEMPLUT SET SB             |

|     | 5.5.15   | Sub block 0x010E – AWR LOOPBACK BURST CONF SET SB 134     |

|     | 5.5.16   | Sub block 0x010F – AWR DYN CHIRP CONF SET SB              |

|     | 5.5.17   | Sub block 0x0110 – AWR_DYN_PERCHIRP_PHASESHIFTER_CONF_    |

|     |          | SET SB                                                    |

|     | 5.5.18   | Sub block 0x0111 – AWR DYN CHIRP ENABLE SB                |

|     | 5.5.19   | Sub block 0x0112 – AWR_INTERCHIRP_BLOCKCONTROLS_SB 147    |

|     | 5.5.20   | Sub block 0x0113 – AWR_SUBFRAME_START_CONF_SB             |

|     | 5.5.21   | Sub block 0x0115 – AWR_ADVANCE_CHIRP_CONF_SB              |

|     | 5.5.22   | Sub block 0x0116 – AWR_ADVANCE_CHIRP_GENERIC_LUT_LOAD_    |

|     |          | SB                                                        |

|     | 5.5.23   | Sub block 0x0117 – AWR_MONITOR_TYPE_TRIG_CONF_SB 170      |

|     | 5.5.24   | Sub block 0x0118 – AWR_ADVANCE_CHIRP_DYN_LUT_ADDR_OFFSET_ |

|     |          | CFG_SB                                                    |

| 5.6 | Sub bloo | cks related to AWR_RF_DYNAMIC_CONF_GET_SB                 |

|     | 5.6.1    | Sub block 0x0120 – AWR_PROFILE_CONF_GET_SB                |

|     | 5.6.2    | Sub block 0x0121 – AWR_CHIRP_CONF_GET_SB                  |

|     | 5.6.3    | Sub block 0x0122 – AWR_FRAME_CONF_GET_SB                  |

|     | 5.6.4    | Sub block 0x0123 – RESERVED                               |

|     | 5.6.5    | Sub block 0x0124 – RESERVED                               |

|     | 5.6.6    | Sub block 0x0125 – AWR_ADV_FRAME_CONF_GET_SB              |

|     | 5.6.7    | Sub block 0x0126 – RESERVED                               |

|     | 5.6.8    | Sub block 0x0127 – RESERVED                               |

|     | 5.6.9    | Sub block 0x0128 – RESERVED                               |

|     |          |                                                           |

|      | 5.6.10   | Sub block 0x0129 – RESERVED                            | . 177 |

|------|----------|--------------------------------------------------------|-------|

|      | 5.6.11   | Sub block 0x012A – RESERVED                            | . 177 |

|      | 5.6.12   | Sub block 0x012B – RESERVED                            | . 177 |

|      | 5.6.13   | Sub block 0x012C – AWR_RX_GAIN_TEMPLUT_GET_SB          | . 177 |

|      | 5.6.14   | Sub block 0x012D – AWR_TX_GAIN_TEMPLUT_GET_SB          | . 178 |

| 5.7  | Sub bloc | ks related to AWR_FRAME_TRIG_MSG                       | . 178 |

|      | 5.7.1    | Sub block 0x0140 – AWR_FRAMESTARTSTOP_CONF_SB          | . 178 |

| 5.8  | Sub bloc | ks related to AWR_RF_ADVANCED_FEATURES_CONF_SET_MSG .  | . 179 |

|      | 5.8.1    | Sub block 0x0180 - AWR_BPM_COMMON_CONF_SET_SB          | . 179 |

|      | 5.8.2    | Sub block 0x0181 – AWR_BPM_CHIRP_CONF_SET_SB           | . 180 |

| 5.9  | Sub bloc | ks related to AWR_RF_STATUS_GET_MSG                    | . 181 |

|      | 5.9.1    | Sub block 0x0220 – AWR_RF_VERSION_GET_SB               | . 181 |

|      | 5.9.2    | Sub block 0x0221 – AWR_RF_CPUFAULT_STATUS_GET_SB       | . 183 |

|      | 5.9.3    | Sub block 0x0222 – AWR_RF_ESMFAULT_STATUS_GET_SB       | . 184 |

|      | 5.9.4    | Sub block 0x0223 – AWR_RF_DIEID_GET_SB                 | . 187 |

|      | 5.9.5    | Sub block 0x0224 – AWR_RF_BOOTUPBIST_STATUS_GET_SB     | . 188 |

| 5.10 | Sub bloc | ks related to AWR_RF_MONITORING_REPORT_GET_MSG         | . 190 |

|      | 5.10.1   | Sub block 0x0260 – AWR_RF_DFE_STATISTICS_REPORT_GET_SB | . 190 |

| 5.11 | Sub bloc | ks related to AWR_RF_MISC_CONF_SET_MSG                 | . 198 |

|      | 5.11.1   | Sub block 0x02C0 – RESERVED                            | . 198 |

|      | 5.11.2   | Sub block 0x02C1 – RESERVED                            | . 198 |

|      | 5.11.3   | Sub block 0x02C2 - AWR_RF_TEST_SOURCE_CONFIG_SET_SB .  | . 198 |

|      | 5.11.4   | Sub block 0x02C3 - AWR_RF_TEST_SOURCE_ENABLE_SET_SB .  | . 201 |

|      | 5.11.5   | Sub block 0x02C4 – 0x02CB RESERVED                     | . 201 |

|      | 5.11.6   | Sub block 0x02CC – AWR_RF_LDO_BYPASS_SB                | . 201 |

|      | 5.11.7   | Sub block 0x02CD – AWR_RF_PALOOPBACK_CFG_SB            | . 203 |

|      | 5.11.8   | Sub block 0x02CE – AWR_RF_PSLOOPBACK_CFG_SB            | . 204 |

|      | 5.11.9   | Sub block 0x02CF – AWR_RF_IFLOOPBACK_CFG_SB            | . 206 |

|      | 5.11.10  | Sub block 0x02D0 – AWR_RF_GPADC_CFG_SET_SB             | . 207 |

|      | 5.11.11  | Sub block 0x02D1 – RESERVED                            |       |

|      | 5.11.12  | Sub block 0x02D2 – RESERVED                            | . 210 |

|      |          | Sub block 0x02D3 – RESERVED                            |       |

| 5.12 | Sub bloc | ks related to AWR_RF_MISC_CONF_GET_MSG                 | . 210 |

|      | 5.12.1   | Sub block 0x02E0 to 0x2E9 – RESERVED                   | . 210 |

|      | 5.12.2   | Sub block 0x02EA – AWR_RF_TEMPERATURE_GET_SB           | . 210 |

| 5.13 | Sub bloc | ks related to AWR_RF_ASYNC_EVENT_MSG1                  | . 211 |

|      | 5.13.1   | Sub block 0x1000 – RESERVED                            | . 212 |

|      | 5.13.2   | Sub block 0x1001 – RESERVED                            | . 212 |

|      | 5.13.3   | Sub block 0x1002 – AWR_AE_RF_CPUFAULT_SB               | . 212 |

|      | 5.13.4   | Sub block 0x1003 – AWR_AE_RF_ESMFAULT_SB               | . 214 |

|      | 5.13.5   | Sub block 0x1004 – AWR_AE_RF_INITCALIBSTATUS_SB        | . 217 |

|      | 5.13.6   | Sub block 0x1005 – RESERVED                            | . 219 |

|      | 5.13.7   | Sub block 0x1006 – RESERVED                            | . 219 |

|      | 5.13.8   | Sub block 0x1007 – RESERVED                            | . 219 |

|      | 5.13.9  | Sub block 0x1008 – RESERVED                              | 219 |

|------|---------|----------------------------------------------------------|-----|

|      | 5.13.10 | Sub block 0x1009 – RESERVED                              | 219 |

|      | 5.13.11 | Sub block 0x100A - AWR_AE_RF_MONITOR_TYPE_TRIGGER_DONE_  | _   |

|      |         | SB                                                       | 219 |

|      | 5.13.12 | Sub block 0x100B – AWR_AE_RF_FRAME_TRIGGER_RDY_SB        | 220 |

|      | 5.13.13 | Sub block 0x100C - AWR_AE_RF_GPADC_RESULT_DATA_SB        | 220 |

|      | 5.13.14 | Sub block 0x100E – RESERVED                              | 222 |

|      | 5.13.15 | Sub block 0x100D – RESERVED                              | 222 |

|      | 5.13.16 | Sub block 0x100E – RESERVED                              | 222 |

|      | 5.13.17 | Sub block 0x100F - AWR_FRAME_END_AE_SB                   | 222 |

|      | 5.13.18 | Sub block 0x1010 - AWR_ANALOGFAULT_AE_SB                 | 222 |

|      | 5.13.19 | Sub block 0x1011 - AWR_CAL_MON_TIMING_FAIL_REPORT_AE_SB  | 223 |

|      | 5.13.20 | Sub block 0x1012 - AWR_RUN_TIME_CALIB_SUMMARY_REPORT_    |     |

|      |         | AE_SB                                                    | 224 |

|      | 5.13.21 | Sub block 0x1013 - AWR_MONITOR_RF_DIG_LATENTFAULT_REPORT | _   |

|      |         | AE_SB                                                    |     |

|      | 5.13.22 | Sub block 0x1014 – RESERVED                              |     |

|      | 5.13.23 | Sub block 0x1015 – AWR_MONITOR_REPORT_HEADER_AE_SB       | 228 |

|      | 5.13.24 | Sub block 0x1016 - AWR_MONITOR_RF_DIG_PERIODIC_REPORT_   |     |

|      |         | AE_SB                                                    | 229 |

|      | 5.13.25 | Sub block 0x1017 – AWR_MONITOR_TEMPERATURE_REPORT_AE_    |     |

|      |         | SB                                                       | 229 |

|      | 5.13.26 | Sub block 0x1018 - AWR_MONITOR_RX_GAIN_PHASE_REPORT_     |     |

|      |         | AE_SB                                                    | 231 |

|      | 5.13.27 |                                                          |     |

|      |         | AE_SB                                                    |     |

|      | 5.13.28 | Sub block 0x101A – AWR_MONITOR_RX_IFSTAGE_REPORT_AE_SB   |     |

|      | 5.13.29 | Sub block 0x101B – AWR_MONITOR_TX0_POWER_REPORT_AE_SB    |     |

|      | 5.13.30 | Sub block 0x101C - AWR_MONITOR_TX1_POWER_REPORT_AE_SB    |     |

|      | 5.13.31 | Sub block 0x101D - AWR_MONITOR_TX2_POWER_REPORT_AE_SB    | 242 |

|      | 5.13.32 | Sub block 0x101E - AWR_MONITOR_TX0_BALLBREAK_REPORT_     |     |

|      |         | AE_SB                                                    | 243 |

|      | 5.13.33 |                                                          |     |

|      |         | SB                                                       | -   |

| 5.14 |         | ks related to AWR_RF_ASYNC_EVENT_MSG2                    |     |

|      | 5.14.1  | Sub block 0x1020 – AWR_MONITOR_TX2_BALLBREAK_REPORT_AE_  |     |

|      |         | SB                                                       | 244 |

|      | 5.14.2  | Sub block 0x1021 – AWR_MONITOR_TX_GAIN_PHASE_MISMATCH_   |     |

|      |         | REPORT_AE_SB                                             |     |

|      | 5.14.3  | Sub block 0x1022 - AWR_MONITOR_TX0_PHASE_SHIFTER_REPORT  |     |

|      |         | AE_SB                                                    |     |

|      | 5.14.4  | Sub block 0x1023 - AWR_MONITOR_TX1_PHASE_SHIFTER_REPORT  |     |

|      |         | AE_SB                                                    | 250 |

|      | 5.14.5   | Sub block 0x1024 – AWR_MONITOR_TX2_PHASE_SHIFTER_REPORT_<br>AE_SB       |     |

|------|----------|-------------------------------------------------------------------------|-----|

|      | 5.14.6   | Sub block 0x1025 – AWR_MONITOR_SYNTHESIZER_FREQUENCY_                   |     |

|      |          | REPORT_AE_SB                                                            |     |

|      | 5.14.7   | Sub block 0x1026 – AWR_MONITOR_EXTERNAL_ANALOG_SIGNALS_<br>REPORT AE SB |     |

|      | 5.14.8   | Sub block 0x1027 – AWR_MONITOR_TX0_INTERNAL_ANALOG_SIGNA                | LS  |

|      |          | REPORT AE SB                                                            |     |

|      | 5.14.9   | Sub block 0x1028 – AWR_MONITOR_TX1_INTERNAL_ANALOG_SIGNA                | LS  |

|      |          | REPORT AE SB                                                            |     |

|      | 5.14.10  | Sub block 0x1029 - AWR_MONITOR_TX2_INTERNAL_ANALOG_SIGNA                | LS  |

|      |          | REPORT AE SB                                                            |     |

|      | 5.14.11  | Sub block 0x102A - AWR MONITOR RX INTERNAL ANALOG SIGNAL                | S   |

|      |          | REPORT AE SB                                                            |     |

|      | 5.14.12  | Sub block 0x102B – AWR MONITOR PMCLKLO INTERNAL ANALOG                  |     |

|      |          | SIGNALS REPORT AE SB                                                    |     |

|      | 5.14.13  | Sub block 0x102C – AWR MONITOR GPADC INTERNAL ANALOG                    |     |

|      |          | SIGNALS REPORT AE SB                                                    | 262 |

|      | 5.14.14  | Sub block 0x102D -AWR MONITOR PLL CONTROL VOLTAGE REPO                  |     |

|      |          | AE SB                                                                   |     |

|      | 5.14.15  | Sub block 0x102E – AWR MONITOR DUAL CLOCK COMP REPORT                   |     |

|      |          | AE SB                                                                   |     |

|      | 5.14.16  | Sub block 0x1031 – AWR MONITOR RX MIXER IN POWER REPORT                 |     |

|      |          | AE_SB                                                                   | _   |

|      | 5.14.17  | Sub block 0x1033 – AWR_MONITOR_SYNTHESIZER_FREQUENCY_                   |     |

|      |          | NONLIVE_REPORT_AE_SB                                                    | 267 |

| 5.15 | Sub bloc | ks related to AWR_DEV_RFPOWERUP_MSG                                     | 269 |

|      | 5.15.1   | Sub block 0x4000 – AWR_DEV_RFPOWERUP_SB                                 | 269 |

| 5.16 | Sub bloc | ks related to AWR_DEV_CONF_SET_MSG                                      | 270 |

|      | 5.16.1   | Sub block 0x4040 - AWR_DEV_MCUCLOCK_CONF_SET_SB                         | 270 |

|      | 5.16.2   | Sub block 0x4041 - AWR_DEV_RX_DATA_FORMAT_CONF_SET_SB . :               | 271 |

|      | 5.16.3   | Sub block 0x4042 - AWR_DEV_RX_DATA_PATH_CONF_SET_SB                     | 272 |

|      | 5.16.4   | Sub block 0x4043 - AWR_DEV_RX_DATA_PATH_LANEEN_SET_SB                   | 275 |

|      | 5.16.5   | Sub block 0x4044 - AWR_DEV_RX_DATA_PATH_CLK_SET_SB                      | 276 |

|      | 5.16.6   | Sub block 0x4045 – AWR_DEV_LVDS_CFG_SET_SB                              | 277 |

|      | 5.16.7   | Sub block 0x4046 - AWR_DEV_RX_CONTSTREAMING_MODE_CONF_                  |     |

|      |          | SET_SB                                                                  | 279 |

|      | 5.16.8   | Sub block 0x4047 – AWR_DEV_CSI2_CFG_SET_SB                              | 280 |

|      | 5.16.9   | Sub block 0x4048 – AWR_DEV_PMICCLOCK_CONF_SET_SB                        | 282 |

|      | 5.16.10  | Sub block 0x4049 – AWR_MSS_PERIODICTESTS_CONF_SB                        | 287 |

|      | 5.16.11  | Sub block 0x404A – AWR_MSS_LATENTFAULT_TEST_CONF_SB                     | 288 |

|      | 5.16.12  | Sub block 0x404B - AWR_DEV_TESTPATTERN_GEN_SET_SB                       | 290 |

|      | 5.16.13  | Sub block 0x404C - AWR_DEV_CONFIGURATION_SET_SB                         | 293 |

|      | 5.16.14  | Sub block 0x404D – AWR_DEV_RF_DEBUG_SIG_SET_SB                          | 294 |

|   |      | 5.16.15  | Sub block 0x404E - AWR_DEV_DEV_HSI_DELAY_DUMMY_CFG_SET_    |   |

|---|------|----------|------------------------------------------------------------|---|

|   |      |          | SB                                                         |   |

|   |      | 5.16.16  | Sub block $0x404F - AWR_DEV_POWERSAVE_MODE_CONFIG_SB$ 29   | 6 |

|   | 5.17 | Sub bloc | ks related to AWR_DEV_CONF_GET_MSG                         |   |

|   |      | 5.17.1   | Sub block 0x4060 - AWR_DEV_MCUCLOCK_GET_SB                 | 8 |

|   |      | 5.17.2   | Sub block 0x4061 - AWR_DEV_RX_DATA_FORMAT_CONF_GET_SB . 29 | 9 |

|   |      | 5.17.3   | Sub block 0x4062 - AWR_DEV_RX_DATA_PATH_CONF_GET_SB 29     | 9 |

|   |      | 5.17.4   | Sub block 0x4063 - AWR_DEV_RX_DATA_PATH_LANEEN_GET_SB . 29 | 9 |

|   |      | 5.17.5   | Sub block 0x4064 - AWR_DEV_RX_DATA_PATH_CLK_GET_SB 30      | 0 |

|   |      | 5.17.6   | Sub block 0x4065 – AWR_DEV_LVDS_CFG_GET_SB                 | 0 |

|   |      | 5.17.7   | Sub block 0x4066 – AWR_DEV_RX_CONTSTREAMING_MODE_CONF_     |   |

|   |      |          | GET_SB                                                     | 0 |

|   |      | 5.17.8   | Sub block 0x4067 – AWR_DEV_CSI2_CFG_GET_SB                 | 0 |

|   |      | 5.17.9   | Sub block 0x4068 – AWR_DEV_PMICCLOCK_CONF_GET_SB 30        | 1 |

|   |      | 5.17.10  | Sub block 0x4069 - AWR_MSS_LATENTFAULT_TEST_CONF_GET_SB30  | 1 |

|   |      | 5.17.11  | Sub block 0x406A - AWR_MSS_PERIODICTESTS_CONF_GET_SB 30    | 1 |

|   |      | 5.17.12  | Sub block 0x406B - AWR_DEV_TESTPATTERN_GEN_GET_SB 30       | 2 |

|   | 5.18 | Sub bloc | ks related to AWR_DEV_FILE_DOWNLOAD_MSG                    | 2 |

|   |      | 5.18.1   | Sub block 0x4080 - AWR_DEV_FILE_DOWNLOAD_SB                | 2 |

|   | 5.19 | Sub bloc | ks related to AWR_DEV_FRAME_CONFIG_APPLY_MSG               | 3 |

|   |      | 5.19.1   | Sub block 0x40C0 – AWR_DEV_FRAME_CONFIG_APPLY_SB 30        | 3 |

|   |      | 5.19.2   | Sub block 0x40C1 - AWR_DEV_ADV_FRAME_CONFIG_APPLY_SB 30    | 3 |

|   | 5.20 | Sub bloc | ks related to AWR_DEV_STATUS_GET_MSG                       |   |

|   |      | 5.20.1   | Sub block 0x40E0 – AWR_MSSVERSION_GET_SB                   |   |

|   |      | 5.20.2   | Sub block 0x40E1 – AWR_MSSCPUFAULT_STATUS_GET_SB 30        |   |

|   |      | 5.20.3   | Sub block 0x40E2 – AWR_MSSESMFAULT_STATUS_GET_SB 30        |   |

|   | 5.21 |          | ks related to AWR_DEV_ASYNC_EVENT_MSG                      |   |

|   |      | 5.21.1   | Sub block 0x5000 – AWR_AE_DEV_MSSPOWERUPDONE_SB 31         |   |

|   |      | 5.21.2   | Sub block 0x5001 – AWR_AE_DEV_RFPOWERUPDONE_SB 31          |   |

|   |      | 5.21.3   | Sub block 0x5002 – AWR_AE_MSS_CPUFAULT_SB                  |   |

|   |      | 5.21.4   | Sub block 0x5003 – AWR_AE_MSS_ESMFAULT_STATUS_SB 31        |   |

|   |      | 5.21.5   | Sub block 0x5004 – RESERVED                                |   |

|   |      | 5.21.6   | Sub block 0x5005 – AWR_AE_MSS_BOOTERRORSTATUS_SB 32        |   |

|   |      | 5.21.7   | Sub block 0x5006 - AWR_AE_MSS_LATENTFAULT_TESTREPORT_SB32  |   |

|   |      | 5.21.8   | Sub block 0x5007 – AWR_AE_MSS_PERIODICTEST_STATUS_SB 32    |   |

|   |      | 5.21.9   | Sub block 0x5008 – AWR_AE_MSS_RFERROR_STATUS_SB 32         |   |

|   |      |          | Sub block 0x5009 – RESERVED                                |   |

|   |      | 5.21.11  | Sub block 0x500A – RESERVED                                |   |

|   |      |          | Sub block 0x500B – RESERVED                                | 7 |

|   |      | 5.21.13  | Sub block 0x500C - AWR_AE_MSS_POWER_SAVE_TRANSITION_       |   |

|   |      |          | DONE_SB                                                    | 7 |

| 6 | ΑΡΙ  | Program  | nming Sequence 32                                          | 8 |

| - | 6.1  |          | evice mode                                                 |   |

|   |      | 3.5      |                                                            | - |

Revision 2.23 - Jul 22, 2022

|   | 6.2<br>6.3<br>6.4 | Continuc  | ed device mode                                                    | 33 |

|---|-------------------|-----------|-------------------------------------------------------------------|----|

| 7 | API               | Error Ha  | andling and Error Codes 3                                         | 37 |

|   | 7.1               |           | r Handling                                                        |    |

|   | 7.2               |           | r Codes                                                           |    |

|   | 7.3               |           | SPI Error codes                                                   |    |

| 8 | Rad               | ar Moni   | toring APIs 3                                                     | 52 |

|   | 8.1               |           | Configurations and Reports                                        | 52 |

|   |                   | 8.1.1     | Sub block 0x01C0 – AWR_MONITOR_RF_DIG_LATENTFAULT_CONF_<br>SB     |    |

|   |                   | 8.1.2     | Sub block 0x01C1 – AWR MONITOR RF DIG PERIODIC CONF SB.3          |    |

|   |                   | 8.1.3     | Sub block 0x01C2 – AWR MONITOR ANALOG ENABLES CONF SB 3           |    |

|   | 8.2               |           |                                                                   |    |

|   | 0.2               | 8.2.1     | Sub block 0x01C3 – AWR MONITOR TEMPERATURE CONF SB                |    |

|   | 8.3               | -         | and Phase Monitor                                                 |    |

|   |                   | 8.3.1     | Sub block 0x01C4 – AWR MONITOR RX GAIN PHASE CONF SB . 3          |    |

|   | 8.4               | RX Noise  | e Monitor                                                         |    |

|   |                   | 8.4.1     | Sub block 0x01C5 - AWR MONITOR RX NOISE FIGURE CONF SB 3          |    |

|   | 8.5               | RX IF St  | age Monitor                                                       |    |

|   |                   | 8.5.1     | Sub block 0x01C6 – AWR MONITOR RX IFSTAGE CONF SB 3               | 66 |

|   | 8.6               | TX Powe   | er Monitor                                                        |    |

|   |                   | 8.6.1     | Sub block 0x01C7 – AWR_MONITOR_TX0_POWER_CONF_SB 3                | 68 |

|   |                   | 8.6.2     | Sub block 0x01C8 – AWR_MONITOR_TX1_POWER_CONF_SB 3                | 69 |

|   |                   | 8.6.3     | Sub block 0x01C9 – AWR_MONITOR_TX2_POWER_CONF_SB 3                | 71 |

|   | 8.7               | TX Ball E | Break Monitor                                                     | 73 |

|   |                   | 8.7.1     | Sub block 0x01CA - AWR_MONITOR_TX0_BALLBREAK_CONF_SB .3           | 73 |

|   |                   | 8.7.2     | Sub block 0x01CB - AWR_MONITOR_TX1_BALLBREAK_CONF_SB . 3          | 74 |

|   |                   | 8.7.3     | Sub block 0x01CC - AWR_MONITOR_TX2_BALLBREAK_CONF_SB . 3          |    |

|   | 8.8               | TX Gain   | and Phase Mismatch Monitoring                                     | 77 |

|   |                   | 8.8.1     | Sub block 0x01CD – AWR_MONITOR_TX_GAIN_PHASE_MISMATCH_<br>CONF_SB | 77 |

|   | 8.9               | TX Phas   | e Shifter Monitor                                                 | 81 |

|   |                   | 8.9.1     | Sub block 0x01CE – AWR_MONITOR_TX0_PHASE_SHIFTER_CONF_<br>SB      | 81 |

|   |                   | 8.9.2     | Sub block 0x01CF – AWR_MONITOR_TX1_PHASE_SHIFTER_CONF_<br>SB      | -  |

|   |                   | 8.9.3     | Sub block 0x01D0 - AWR_MONITOR_TX2_PHASE_SHIFTER_CONF_            |    |

|   | Q 10              | Synthesi  | SB                                                                |    |

|   | 0.10              | 8.10.1    | Sub block 0x01D1 – AWR MONITOR SYNTHESIZER FREQUENCY              | 33 |

|   |                   | 0.10.1    | CONF_SB                                                           | 93 |

|    | 8.11  | External  | Analog Signals Monitor                                   | 396 |

|----|-------|-----------|----------------------------------------------------------|-----|

|    |       |           | Sub block 0x01D2 - AWR_MONITORING_EXTERNAL_ANALOG_SIGNAL | _   |

|    |       |           | CONF_SB                                                  |     |

|    | 8.12  |           | Analog Signals Monitor                                   |     |

|    |       |           | Sub block 0x01D3 – AWR_MONITOR_TX0_INTERNAL_ANALOG_SIGNA |     |

|    |       |           | CONF_SB                                                  |     |

|    |       |           | Sub block 0x01D4 - AWR_MONITOR_TX1_INTERNAL_ANALOG_SIGNA |     |

|    |       |           |                                                          |     |

|    |       |           | Sub block 0x01D5 – AWR_MONITOR_TX2_INTERNAL_ANALOG_SIGNA |     |

|    |       |           | Sub block 0x01D6 – AWR MONITOR RX INTERNAL ANALOG SIGNAL |     |

|    |       |           | CONF SB                                                  | _   |

|    |       |           | Sub block 0x01D7 – AWR MONITOR PMCLKLO INTERNAL ANALOG   |     |

|    |       |           | SIGNALS CONF SB                                          |     |

|    |       |           | Sub block 0x01D8 – AWR_MONITOR_GPADC_INTERNAL_ANALOG_    |     |

|    |       |           | SIGNALS_CONF_SB                                          | 405 |

|    | 8.13  | PLL Cont  | trol Voltage Monitor                                     | 405 |

|    |       |           | Sub block 0x01D9 - AWR_MONITOR_PLL_CONTROL_VOLTAGE_SIGNA |     |

|    |       |           | CONF_SB                                                  |     |

|    | 8.14  |           | ck Comparator Based Clock Frequency Monitor              | 107 |

|    |       |           | Sub block 0x01DA – AWR_MONITOR_DUAL_CLOCK_COMP_CONF_     | 100 |

|    | 0 1 5 |           | SB                                                       |     |

|    | 0.15  |           | Sub block 0x01DB – AWR_MONITOR_RX_SATURATION_DETECTOR_   | +09 |

|    |       |           | CONF SB                                                  | 109 |

|    |       |           | Sub block 0x01DC – AWR MONITOR SIG IMG MONITOR CONF SB   |     |

|    | 8.16  |           | rinput power monitor                                     |     |

|    |       |           | Sub block 0x01DD – AWR_MONITOR_RX_MIXER_IN_POWER_CONF_   |     |

|    |       |           | SB                                                       | 113 |

|    | 8.17  | Sub block | k 0x01DE – RESERVED                                      | 415 |

|    | 8.18  | •         | ault injection                                           |     |

|    |       | 8.18.1    | Sub block 0x01DF - AWR_ANALOG_FAULT_INJECTION_CONF_SB .4 | 115 |

| 9  | llns  | unnorte   | d Features/APIs and Debug APIs                           | 122 |

| Č  | 9.1   |           | rted Features/APIs and Debug APIs                        |     |

|    |       |           |                                                          |     |

| 10 |       | -         |                                                          | 123 |

|    |       |           | rameters data                                            |     |

|    | 10.2  |           | ality data                                               |     |

|    |       |           | CQ1                                                      |     |

|    |       | 10.2.2    | 0                                                        | +∠9 |

| 11 | Chi   | p, Burst  | and Frame timings                                        | 132 |

|    | 11.1  | Chirp Cyc | cle Time                                                 | 132 |

|    |      |           | Inter Burst   |           |        |       |       |      |       |      |      |      |     |   |       |   |       |     |     |

|----|------|-----------|---------------|-----------|--------|-------|-------|------|-------|------|------|------|-----|---|-------|---|-------|-----|-----|

| 12 | Cali | bration a | and monit     | oring o   | lura   | tion  | s     |      |       |      |      |      |     |   |       |   |       | 4   | 137 |

|    | 12.1 | Boot time | e calibration | duratio   | ns     |       |       |      |       |      |      |      |     |   |       |   |       | 4   | 137 |

|    | 12.2 | Run time  | calibration   | duration  | ns.    |       |       |      |       |      |      |      |     |   |       |   |       | 4   | 138 |

|    | 12.3 | Monitorin | ng duration   |           |        |       |       |      |       |      |      |      |     |   |       |   |       | 4   | 139 |

|    | 12.4 | Software  | overheads     |           |        |       |       |      |       |      |      |      |     |   |       |   |       | 4   | 143 |

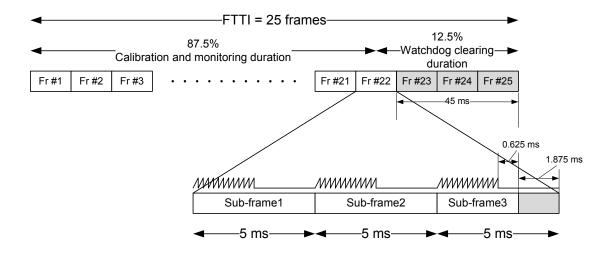

|    |      | 12.4.1    | Note on idl   | e time f  | or cle | aring | g the | e wa | atch  | idog | ) (N | /DT  | ).  |   |       |   |       | 4   | 143 |

|    |      | 12.4.2    | Examples      | for calib | ratior | ns/m  | onito | orin | g tir | ne l | bud  | geti | ing |   |       |   |       | 4   | 145 |

|    | 12.5 | Sample /  | Application   |           | •••    |       |       | • •  |       | • •  | • •  |      |     | • | <br>· | • | <br>• | • • | i   |

| Ap | peno | dices     |               |           |        |       |       |      |       |      |      |      |     |   |       |   |       |     | ii  |

| A  | AW   | R2243 A   | PI change     | S         |        |       |       |      |       |      |      |      |     |   |       |   |       |     | iii |

| В  | xWF  | R6243 AI  | PI change     | S         |        |       |       |      |       |      |      |      |     |   |       |   |       |     | vi  |

## List of Figures

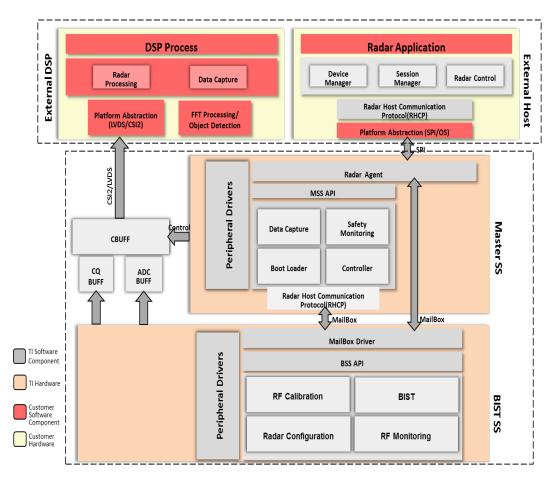

| 2.1   | AWR12xx, AWR22xx, AWR62xx Software Architecture                               | 4 |

|-------|-------------------------------------------------------------------------------|---|

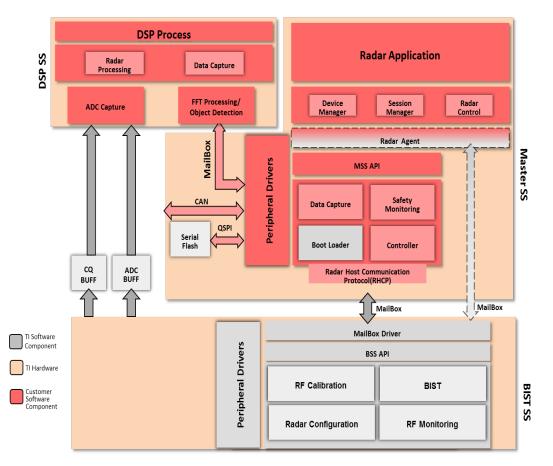

| 2.2   | xWR16xx, xWR18xx and IWR68xx Software Architecture                            | 5 |

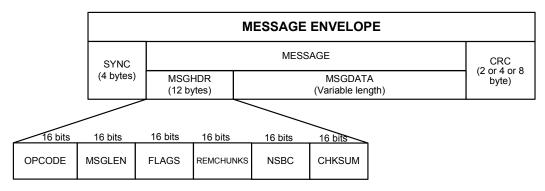

| 2.3   | Radar Message Structure                                                       | 5 |

| 2.4   | Message Header Format                                                         | 6 |

| 2.5   | OPCODE Format                                                                 | 7 |

| 2.6   | MSGLEN Format                                                                 | 0 |

| 2.7   | FLAGS Format                                                                  | 0 |

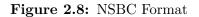

| 2.8   | NSBC Format                                                                   | 1 |

| 2.9   | Message Sub block structure                                                   | 3 |

| 3.1   | Flow Diagram (API)                                                            |   |

| 3.2   | Flow Diagram (Asynchronous Events) 1                                          |   |

| 3.3   | SPI Message Sequence                                                          | 9 |

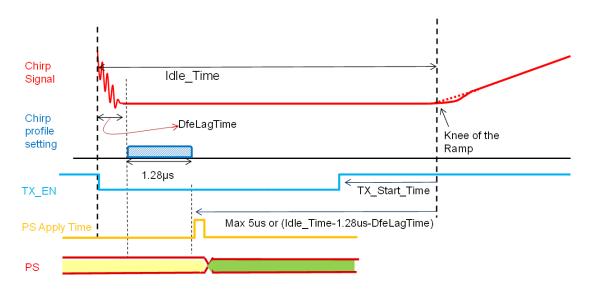

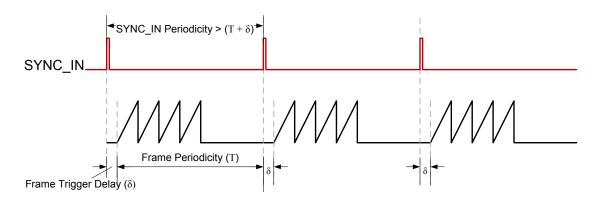

| 5.1   | TX PS apply timing in a chirp                                                 | 7 |

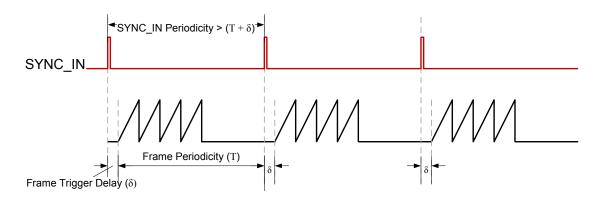

| 5.2   | Frame trigger delay in case of external hardware trigger                      | 4 |

| 5.3   | Frame trigger delay in case of external hardware trigger                      | 9 |

| 5.4   | TX PS apply timing in a chirp                                                 | 1 |

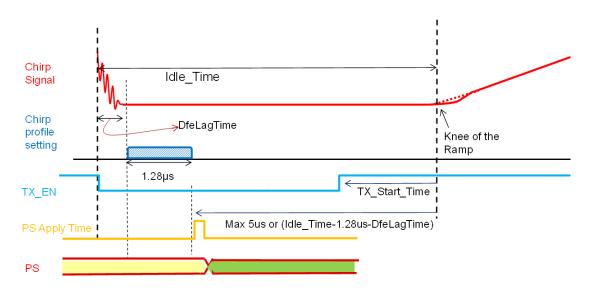

| 5.5   | Dynamic chirp configuration use case timing diagram                           | 7 |

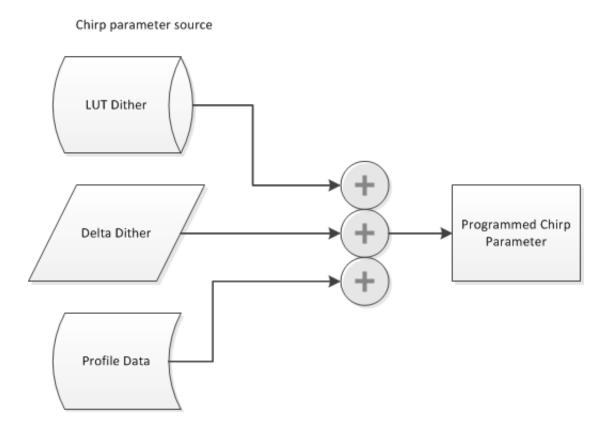

| 5.6   | Advance chirp parameter dither sources and program                            | 1 |

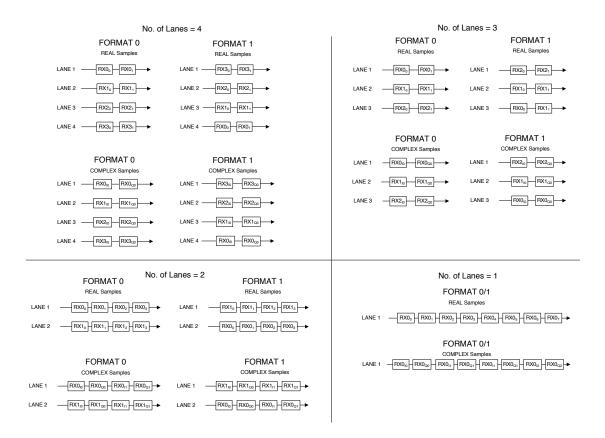

| 5.7   | Lane formats and the order of receiving the data from the lanes               |   |

| 5.8   | Power save entry exit sequence                                                | 6 |

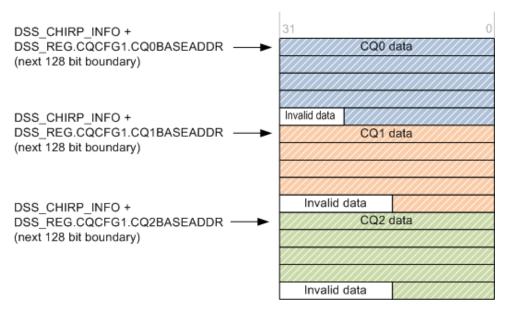

| 10.1  |                                                                               |   |

|       | Chirp parameter information from DSS registers                                |   |

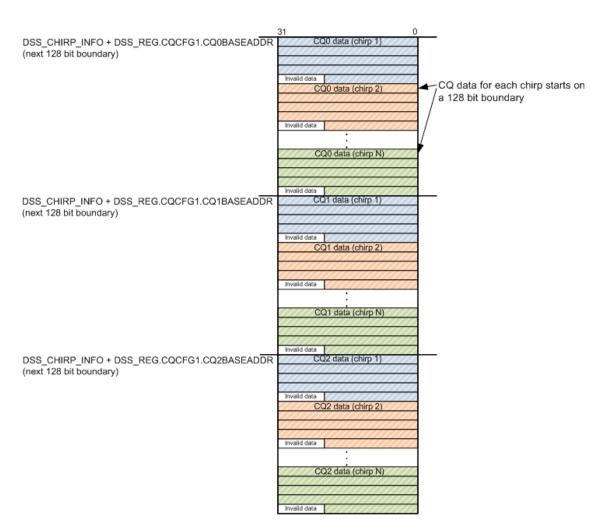

|       | CQ data start address configuration in single chirp use case                  |   |

|       | CQ data start address configuration in multi chirp use case                   |   |

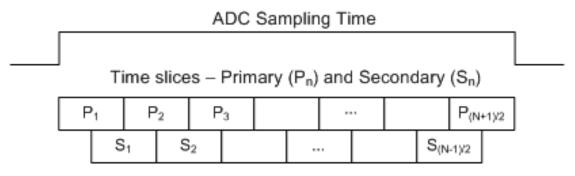

|       | Time slices during RX signal and image band monitor and saturation monitor 42 |   |

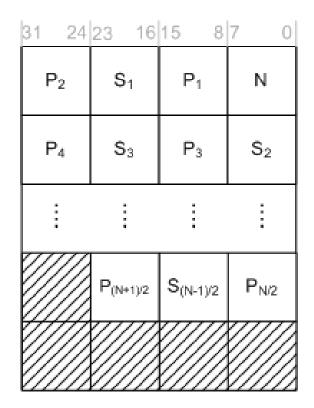

|       | CQ1 data format in memory in 16-bit mode                                      |   |

|       | CQ1 data format in memory in 12-bit mode                                      |   |

|       | CQ1 data format in memory in 14-bit mode                                      |   |

|       | CQ2 data format in memory in 16-bit mode                                      |   |

|       | OCQ2 data format in memory in 12-bit mode                                     |   |

| 10.11 | ICQ2 data format in memory in 14-bit mode                                     | 1 |

| 12.1  | Watchdog idle time calculation                                                | 4 |

### List of Tables

| 1.1                                                                                      | TI CMOS mmWave radar devices                                  | 2        |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------|

| <ol> <li>2.1</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> </ol> | Possible SYNC values and their usage                          | 10<br>10 |

| 4.1                                                                                      | Summary of all Radar messages and their associated sub blocks | 21       |

| 5.1<br>5.2                                                                               | AWR_RESP_ERROR_SB contents                                    |          |

| 5.3                                                                                      | AWR ADCOUT CONF SB contents                                   |          |

| 5.4                                                                                      | AWR_LOWPOWERMODE_CONF_SET_SB contents                         |          |

| 5.5                                                                                      | AWR_DYNAMICPOWERSAVE_CONF_SET_SB contents                     |          |

| 5.6                                                                                      | AWR_HIGHSPEEDINTFCLK_CONF_SET_SB contents                     |          |

| 5.7                                                                                      | AWR_RF_DEVICE_CFG_SB contents                                 |          |

| 5.8                                                                                      | AWR_RF_MISC_CTL_SB contents                                   | 59       |

| 5.9                                                                                      | AWR_CAL_MON_FREQUENCY_LIMITS_SB contents                      |          |

|                                                                                          | AWR_RF_INIT_CALIBRATION_CONF_SB contents                      |          |

|                                                                                          | AWR_CAL_MON_FREQUENCY_TX_POWER_LIMITS_SB contents             |          |

|                                                                                          | AWR_CAL_DATA_RESTORE_SB contents                              |          |

|                                                                                          | AWR_PHASE_SHIFTER_CAL_DATA_RESTORE_SB contents                |          |

|                                                                                          | Typical APLL and Synth BW settings for xWR6x43                |          |

|                                                                                          | Typical APLL and Synth BW settings for AWR2243                |          |

|                                                                                          | AWR_APLL_SYNTH_BW_CONTROL_SB contents                         |          |

|                                                                                          | AWR_CAL_DATA_SAVE_SB contents                                 |          |