www.ti.com January 2021

# PRU-ICSS EtherCAT Slave Firmware Data Sheet

### **FEATURES**

- All EtherCAT Commands (NOP, APRD, APWR, APRW, FPRD, FPWR, FPRW, BRD, BWR, BRW, LRD, LWR, LRW, ARMW and FRMW)

- 8 FMMU support

- 8 SM support

- 8KB(AM335, AMIC110) /28KB (AMIC120, AM437, AM57) /59KB (AM65x, AM64x) of Process Data RAM

- Distributed clocks (DC)

- o 64-bit DC

- SYNC0 out generation single shot and cyclic mode support

- SYNC1 out generation SYNC1 cycle time multiple of SYNC0 cycle time

- Latch0 and Latch1 inputs

- System Time PDI control

- DL Loop Control

- Using MII\_RX\_LINK (fast depending on PHY link loss detection latency) – mandatory for cable redundancy support

- Using PRU-ICSS MDIO state machine – not recommended for cable redundancy support

- Interrupts AL and ECAT events

- SYNC0, SYNC1 and PDI interrupt events on external SOC pins

- Watchdog PDI and SM

- Error Counters

- RX Invalid Frame Counter Port 0/1

- RX ERR Counter Port 0/1

- Forwarded Error Counter Port 0/1

- ECAT Processing Unit Error Counter

- LED Run, Error and Port0/1 activity based on firmware feedback

- Controlled via GPIO from Host

CPU based on firmware feedback

or by PHY directly

- EEPROM Emulation for ESI EPPROM support

- External flash for non-volatile storage support

- Management Interface for PHY over EtherCAT

- PHY address configuration and host side PRU-ICSS MDIO API for PHY programming

- Cable Redundancy support

- TI-ESC SPI Slave mode support (based on ET1100 protocol)

- On-chip memory execution support (without DDR)

- Enhanced Process Data Interface with EDMA support

- CiA402 Drive profile based Single-chip motor control support

- Reset isolation support on AM64x

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

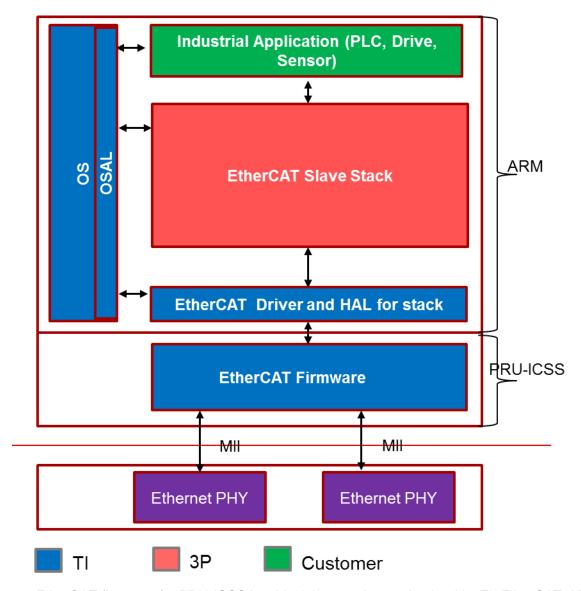

### Description

PRU-ICSS EtherCAT Software from TI can be used by customers to add EtherCAT function on top of Processor SDK to Sitara processors .PRU-ICSS EtherCAT firmware implements EtherCAT slave controller layer2 functionality with two MII ports (one IN and one OUT port per PRU-ICSS) in accordance with ETG1000 specification [5]. This provides EtherCAT slave ASIC like functionality integrated into Sitara Processors with PRU-ICSS IP.

EtherCAT firmware for PRU-ICSS is a black box product maintained by TI. EtherCAT driver allows loading and running the EtherCAT firmware and acts as an interface with ESC firmware. This also includes PDI/Hardware abstraction layer (HAL) for popular EtherCAT stacks. EtherCAT driver is provided in full source so that customers can adapt this implementation to own hardware and Operating Systems.

EtherCAT Slave Stack typically consists of PDI/HAL, EtherCAT stack and user application which can be

#### www.ti.com

customized. The behavior of the generic EtherCAT stack is described in ETG.1000 Specification [6]. Key components are EtherCAT state machine, real time Process Data Interface and Mailbox interface which provides non-real time interfaces like (AoE, CoE, EoE, FoE and SoE).

# Performance Benchmarking: Cycle Time

The application was benchmarked for performance to figure out the lowest cycle time with which a given board can function. Benchmarking was done with 3 Boards running full mode application connected with Distributed Clocks (SYNC0) enabled and CoE data in "Auto-update" for all Objects. TwinCAT Master was used as the EtherCAT master for these tests. Below data is the lowest tested cycle time, cycle time lower that this might be possible depending on the loading and CPU operational frequency.

| SOC/Board             | ARM CPU<br>Frequency | Lowest Cycle time (tested) | Remarks                                   |

|-----------------------|----------------------|----------------------------|-------------------------------------------|

| AMIC11x / iceAMIC110  | 300 MHz              | 62.5 us                    | Tested in DC mode with CoE update enabled |

| AM335x / AM335x ICEv2 | 600 MHz              | 62.5 us                    | Tested in DC mode with CoE update enabled |

| AM437x / AM437x IDK   | 600 MHz              | 50 us                      | Tested in DC mode with CoE update enabled |

| AM57xx / AM57xx IDK   | 1 GHz                | 31.25 us                   | Tested in DC mode with CoE update enabled |

| AM65xx / AM65xx IDK   | 800 MHz              | 31.25 us                   | Tested in DC mode with CoE update enabled |

| AM64x                 | 800 MHz              | 50 us                      | Tested in DC mode                         |

## **Performance Benchmarking: Interrupt Processing Time**

The application was benchmarked for performance to figure out the interrupt processing time for PDI and Sync ISRs. Benchmarking was done with 1 board running full mode application connected with Distributed Clocks (SYNC0) enabled. TwinCAT Master was used as the EtherCAT master for these tests. The cycle time was 50 us. Below data is the maximum time taken for PDI ISR and Sync ISR processing.

| SOC/Board | ARM CPU<br>Frequency | Cycle Time | PDI ISR Processing Time | Sync ISR Processing Time |

|-----------|----------------------|------------|-------------------------|--------------------------|

| AM64x     | 800 MHz              | 50 us      | 7.860 us                | 9.120 us                 |

# **Performance Benchmarking: DC SYNC Jitter**

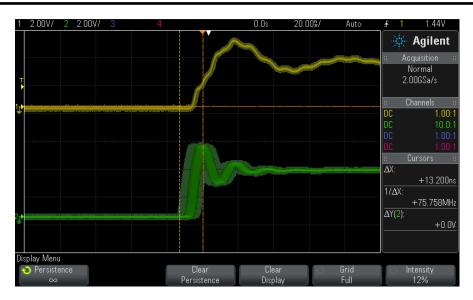

The application was benchmarked for performance to figure out the worst case SYNC pulse jitter observed when boards are connected with Distributed Clock (SYNC0) enabled. The readings were taken with Boards running at 100us Cycle time (10000 packets/sec).

| No. | Board Topology                               | Highest SYNC Pulse Jitter |

|-----|----------------------------------------------|---------------------------|

| 1   | TwinCAT Master <-> AM335x ICE <-> AM335x ICE | 13.2 ns                   |

Topology (1) oscilloscope capture showing Sync Pulse jitter measurement between two AM335x ICE boards

## Performance Benchmarking: Enhanced Process Data Interface with EDMA Results

Read and write access latency for sync manager buffers in Process Data was measure for this benchmarking. The below improvements are measured using the maximum access latency recorded on AM437x IDK.

| Process Data action | Max time in legacy application | Max time in<br>Enhanced<br>application | Improvement | Buffer Location         |

|---------------------|--------------------------------|----------------------------------------|-------------|-------------------------|

| Read 253 bytes      | 25.4 µs                        | 3.8 µs                                 | 6.5x        | DDR (cached)            |

| Write 263 bytes     | 6.7 μs                         | 1.9 µs                                 | 3.5x        | onChip RAM (non-Cached) |

| Read 5 bytes        | 1.9 µs                         | 1.2 µs                                 | 1.5x        | onChip RAM (non-Cached) |

| Write 7 bytes       | 2.4 µs                         | 0.7 µs                                 | 3x          | onChip RAM (non-Cached) |

### **Performance Summary**

A 300 MHz CPU speed is sufficient to support a simple IO or sensor application. More complex applications can use higher speed grades of up to 1.5 GHz depending on the SoC. The PRU core speed remains 200 MHz for all speed grades. AM572x IDK running default EtherCAT application (5 bytes output and 7 bytes input) on Cortex-A15 at nominal OPP (1GHz) can communicate with PLC at cycle time as low as 31.25  $\mu$ s with Distributed Clocks (SYNC0) enabled

# **Memory Summary**

This section describes memory usage of the EtherCAT PRU-ICSS firmware

# **Table 1 EtherCAT PRU-ICSS Firmware Memory Statistics**

| Memory              | AM335x/AMIC110 | AM437x/AM57xx | AM65xx/AM64x | Remarks                                                         |

|---------------------|----------------|---------------|--------------|-----------------------------------------------------------------|

| PRU-ICSS Shared RAM | 12 KB          | 32 KB         | 63 KB        | 4KB Register memory and<br>8KB/28KB/59KB Process Data<br>memory |

# **Hardware Requirements**

Sitara Processor with PRU-ICSS IP and EtherCAT support

• ESC implementation uses following interrupts mapped to Host Interrupt Controller say GIC

| Stack/application interrupts        |                  |                                             |  |

|-------------------------------------|------------------|---------------------------------------------|--|

| ESC firmware Host Interrupt Remarks |                  |                                             |  |

| interrupt                           |                  |                                             |  |

| DC SYNC0 OUT                        | PRU_ICSS_EVTOUT1 | Used in DC mode for syncing the application |  |

| DC SYNC1 OUT                        | PRU_ICSS_EVTOUT2 | Used in DC mode for syncing the application |  |

| PDI Interrupt                       | PRU_ICSS_EVTOUT3 | AL event/PDI interrupt to host stack        |  |

| ESC command ACK                     | PRU_ICSS_EVTOUT4 | ESC firmware command completion ACK to Host |  |

- ESC implementation makes use of one instance of HW spinlock (SPINLOCK\_LOCK\_REG0)

- HW signals required to implement EtherCAT slave functionality is shown below, this info needs to be used in conjunction with <a href="http://www.ti.com/tool/PINMUXTOOL">http://www.ti.com/tool/PINMUXTOOL</a>

NOTE: w.r.t prX, X is 1 or 2 (respectively PRU-ICSS1 or PRU-ICSS2 - refer to SOC TRM for availability)

Table 2 PRU-ICSS signals required for EtherCAT functionality

| Signal name            |                   | Description                  |  |

|------------------------|-------------------|------------------------------|--|

| PRU-ICSS MDIO          |                   |                              |  |

| prX_mdio_mdclk         | Mandatory         | MDIO clock                   |  |

| prX_mdio_data          | Mandatory         | MDIO data                    |  |

| PRU-ICSS MII PORTO (IN | PORT) and PRU-ICS | SS MII PORT1 (OUT PORT)      |  |

|                        |                   |                              |  |

| prX_mii_mt0_clk        | Mandatory         | MIIO and MII1 transmit clock |  |

| prX_mii_mt1_clk        |                   |                              |  |

| prX_mii0_txd3          | Mandatory         | MII0 and MII1 transmit data3 |  |

| prX_mii1_txd3          |                   |                              |  |

| prX_mii0_txd2          | Mandatory         | MII0 and MII1 transmit data2 |  |

| prX_mii1_txd2          |                   |                              |  |

| prX_mii0_txd1          | Mandatory         | MII0 and MII1 transmit data1 |  |

| prX_mii1_txd1          |                   |                              |  |

| prX_mii0_txd0          | Mandatory         | MII0 and MII1 transmit data0 |  |

| prX_mii1_txd0          |                   |                              |  |

| prX_mii0_rxd3          | Mandatory         | MII0 and MII1 receive data3  |  |

| prX_mii1_rxd3          |                   |                              |  |

| prX_mii0_rxd2          | Mandatory         | MII0 and MII1 receive data2  |  |

| prX_mii1_rxd2          |                   |                              |  |

| prX_mii0_rxd1          | Mandatory         | MII0 and MII1 receive data1  |  |

| prX_mii1_rxd1                           |                  |                                                    |  |  |  |

|-----------------------------------------|------------------|----------------------------------------------------|--|--|--|

| prX_mii0_rxd0                           | Mandatory        | MII0 and MII1 receive data0                        |  |  |  |

| prX_mii1_rxd0                           |                  |                                                    |  |  |  |

| prX_mii0_txen                           | Mandatory        | MII0 and MII1 TX enable                            |  |  |  |

| prX_mii1_txen                           |                  |                                                    |  |  |  |

| prX_mii_mr0_clk                         | Mandatory        | MII0 and MII1 receive clock                        |  |  |  |

| prX_mii_mr1_clk                         |                  |                                                    |  |  |  |

| prX_mii0_rxdv                           | Mandatory        | MII0 and MII1 RX data valid                        |  |  |  |

| prX_mii1_rxdv                           |                  |                                                    |  |  |  |

| prX_mii0_rxer                           | Mandatory        | MII0 and MII1 RXERR                                |  |  |  |

| prX_mii1_rxer                           |                  |                                                    |  |  |  |

| prX_mii0_rxlink                         | Recommended      | Enhanced link detection**/Redundancy support -     |  |  |  |

| prX_mii1_rxlink                         |                  | connect LED_LINK/LED_SPEED from PHY                |  |  |  |

| . – –                                   |                  | here                                               |  |  |  |

| PRU-ICSS Distributed Clocks (           | Network clock sv | (nchronization)                                    |  |  |  |

| prX_edc_sync0_out                       | Recommended      | SYNC0 out - Time synchronized OUT0                 |  |  |  |

| 1 ===================================== | (for DC          | , , , , , , , , , , , , , , , , , , , ,            |  |  |  |

|                                         | capable          |                                                    |  |  |  |

|                                         | slaves)          |                                                    |  |  |  |

| prX_edc_sync1_out                       | Optional         | SYNC1 out - Time synchronized OUT1                 |  |  |  |

| 1 ===================================== | '                | (depends on SYNC0)                                 |  |  |  |

| prX_edc_latch0_in                       | Optional         | LATCH0 in (Time stamp latch input0)                |  |  |  |

| prX_edc_latch1_in                       | Optional         | LATCH1 in (Time stamp latch input1)                |  |  |  |

| PRU-ICSS PDI Interrupt                  |                  |                                                    |  |  |  |

| prX_edio_data_out0                      | Optional         | PDI ISR output to external SOC pin (via one of the |  |  |  |

| prX_edio_data_out1                      |                  | 8 PRU-ICSS digio outputs. PDI ISR pin can be       |  |  |  |

| prX_edio_data_out2                      |                  | selected via vendor specific register at offset    |  |  |  |

| prX_edio_data_out3                      | •                | 0xE0A.                                             |  |  |  |

| prX_edio_data_out4                      |                  |                                                    |  |  |  |

| prX_edio_data_out5                      |                  |                                                    |  |  |  |

| prX_edio_data_out6                      |                  |                                                    |  |  |  |

| prX_edio_data_out7                      |                  |                                                    |  |  |  |

|                                         | ESC LED control* |                                                    |  |  |  |

| Any available GPIOs can be used         | Mandatory        | RUN and ERR LED are controlled by stack.           |  |  |  |

| for this purpose. Requires 4            |                  | LED_LINK/ACT0/1 are controlled by Ethernet PHY.    |  |  |  |

| LED_RUN (Green),                        |                  |                                                    |  |  |  |

| LED_ERR(Red),                           |                  |                                                    |  |  |  |

| LED_LINK/ACTO,                          |                  |                                                    |  |  |  |

| LED_LINK/ACT0                           |                  |                                                    |  |  |  |

$<sup>^{\</sup>ast}$ : Refer to ETG.1300 – Indicator and Labeling specification [7] and ETG.9001 – Marking Rules [8] to make sure that product conformance requirement are met

#### www.ti.com

### **Software**

EtherCAT slave firmware, driver, examples and associated documentation for Sitara Processors is available from <a href="http://www.ti.com/tool/PRU-ICSS-ETHERCAT-SLAVE">http://www.ti.com/tool/PRU-ICSS-ETHERCAT-SLAVE</a>. EtherCAT software runs on top of TI Processor SDK

More details are available in the below mentioned links

http://software-dl.ti.com/pru-icss-industrial-sw/esd/docs/indsw/index.html

http://software-dl.ti.com/processor-sdk-rtos/esd/docs/latest/rtos/index.html

http://software-dl.ti.com/processor-sdk-rtos/esd/docs/latest/linux/index.html

### **Certification Information**

Certification was done on <u>AM335x ICEv1</u> board using EtherCAT firmware build (1.2.42) and Beckhoff SSC 5.0.1 EtherCAT slave stack during Feb 2013

#### References

- 1. EtherCAT on Sitara Processors spry187e

- 2. Industrial Communications Solution Guide slyy050b

- 3. EtherCAT Communications Development Platform

- 4. Single Chip Drive for Industrial Communications and Motor Control

- 5. ETG.1000 part 4 Data link Layer protocol specification

- 6. ETG.1000 part 6 Application link Layer protocol specification

- 7. ETG.1300 Indicator and Labelling specification

- 8. ETG.9001 Marking Rules

- 9. EtherCAT ESC datasheet Section I Technology

- 10. EtherCAT ESC datasheet Section 2 Register Description

- 11. <a href="http://processors.wiki.ti.com/index.php/PRU\_ICSS\_EtherCAT\_firmware\_API\_guide#PRU-ICSS\_EtherCAT\_Register\_List">http://processors.wiki.ti.com/index.php/PRU\_ICSS\_EtherCAT\_firmware\_API\_guide#PRU-ICSS\_EtherCAT\_Register\_List</a>

- 12. <u>Beckhoff SSC documentation</u> available as part of ET9300 EtherCAT Slave Stack Code (<a href="http://www.ethercat.org/memberarea/stack\_code.aspx">http://www.ethercat.org/memberarea/stack\_code.aspx</a>)

- 13. EtherCAT Slave Implementation Guide from ETG

- 14. ESD EtherCAT Slave Stack: https://esd.eu/en/products/ethercat-slave

- 15. icECAT Linux SDK from ibv : <a href="http://www.ibv-augsburg.net/media/pdf/icECAT\_Slave\_SDK\_Linux\_Whitepaper.pdf">http://www.ibv-augsburg.net/media/pdf/icECAT\_Slave\_SDK\_Linux\_Whitepaper.pdf</a>

# www.ti.com

# **Acronyms**

| Acronym  | Description                                                        |

|----------|--------------------------------------------------------------------|

| PRUSS    | Programmable RealTime Unit Sub System                              |

| PRU-ICSS | Programmable RealTime Unit - Industrial Communication Sub System - |

|          | PRUSS with industrial communication support                        |

| ESC      | EtherCAT Slave Controller                                          |

| ECAT     | EtherCAT                                                           |

| PDI      | Process Data Interface (Host interface to ESC)                     |

| FMMU     | Fieldbus Memory Management Unit                                    |

| SM       | Sync Manager                                                       |

| SSC      | Slave Stack Code (from Beckhoff)                                   |

| DL       | Datalink Layer                                                     |

| ESI      | EtherCAT Slave Information                                         |

| ISR      | Interrupt Service Routine                                          |

| AL       | Application Layer                                                  |

| LED      | Light Emitting Diode                                               |

| HAL      | Hardware Abstraction Layer                                         |

| AoE      | ADS over EtherCAT                                                  |

| CoE      | CANopen application profile over EtherCAT                          |

| EoE      | Ethernet over EtherCAT                                             |

| FoE      | File Transfer over EtherCAT                                        |

| SoE      | Servo drive profile over EtherCAT                                  |

| PDO      | Process Data Object                                                |

| PLC      | Programmable Logic Controller                                      |

| HAL      | Hardware Abstraction Layer                                         |

| MDIO     | Management Data Input Output                                       |

| MII      | Media Independent Interface                                        |

| ASIC     | Application Specific Integrated Circuit                            |

| OS       | Operating Systems                                                  |

| SoC      | System On Chip                                                     |

| IDK      | Industrial Development Kit (EVM)                                   |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

**Applications**

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy www.ti.com/clocks www.ti.com/industrial Clocks and Timers Industrial Interface interface.ti.com Medical www.ti.com/medical Logic logic.ti.com Security www.ti.com/security Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense www.ti.com/video Microcontrollers microcontroller.ti.com Video and Imaging

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated

**Products**